# GPU Programming Optimization - GSoC 2023 (Cont'd)

Huiyu Xie huiyuxie.sde@gmail.com

The project focused on accelerating the <u>discretization processes used in</u> <u>solving partial differential equations (PDEs)</u> via <u>GPU programming</u>.

Trixi.il

Note: The GPU type selected for this project is the <u>NVIDIA Tesla</u> <u>V100</u>, which features <u>5120 CUDA</u> <u>Cores</u> and <u>640 Tensor Cores</u>. The GPU was set up in the cloud on AWS. Links to some relevant resources:

- Trixi.jl (<u>Docs</u>, <u>GitHub</u>)

- CUDA.jl (<u>Docs</u>, <u>GitHub</u>)

- GSoC 2023 Project (<u>Google</u>, <u>Code</u>, <u>Report</u>)

- CUDA (<u>Docs</u>)

- AWS (<u>Docs</u>)

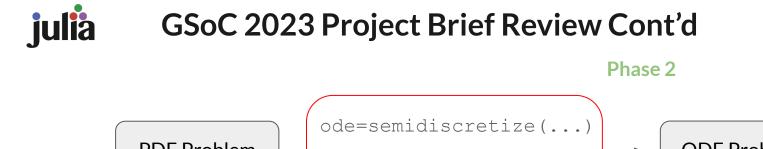

ODEProblem (rhs!, u0 ode, tspan, semi)

When solving the ODE problem...

### GSoC 2023 Project Brief Review Cont'd

Implemented GPU solvers for 1D, 2D and 3D equation problems based on DGSEM with tree mesh.

| Trixi.jl / src / solvers / dgsem_tre | e /                         | rhs         | _gpu!()                                   | for example! |

|--------------------------------------|-----------------------------|-------------|-------------------------------------------|--------------|

| 🗋 dg.jl                              |                             | -           |                                           |              |

| 🕒 dg_1d.jl                           |                             | 1           | <pre>copy_to_gpu!(. cuda volume int</pre> |              |

| dg_1d_parabolic.jl                   |                             |             | cuda_prolong2in                           |              |

| 🗋 dg_2d.jl                           |                             |             | cuda_interface_                           |              |

| dg_2d_compressible_euler.jl          |                             |             | cuda_prolong2bo<br>cuda_boundary_:        |              |

| 🗋 dg_2d_parabolic.jl 🚺               | Current issue is about dat  | ta transfer | cuda_surface_i                            | -            |

| 🗋 dg_2d_parallel.jl                  | and it is simple to optimiz | e.          | cuda_jacobian!<br>cuda sources!(          |              |

| 🗋 dg_2d_subcell_limiters.jl          |                             |             | copy_to_cpu!(.                            |              |

| 🗋 dg_3d.jl                           |                             | end         | (                                         |              |

Tested both CPU and GPU implementation using example <u>elixir\_advection\_basic.jl</u> (2D equation problem), relative errors are shown as below:

julia> extrema(du\_gpu -du\_cpu)./ maximum(abs, du\_cpu) # Based on Float32

```

(-1.707497444828748e-5, 1.7006649665921008e-5)

```

julia> extrema(du\_gpu -du\_cpu)./ maximum(abs, du\_cpu) # Based on Float64

(-3.3923170749628214e-14, 3.61847154662701e-14)

While using Float64 is much better than Float32, both cases caused accuracy issues. Why?

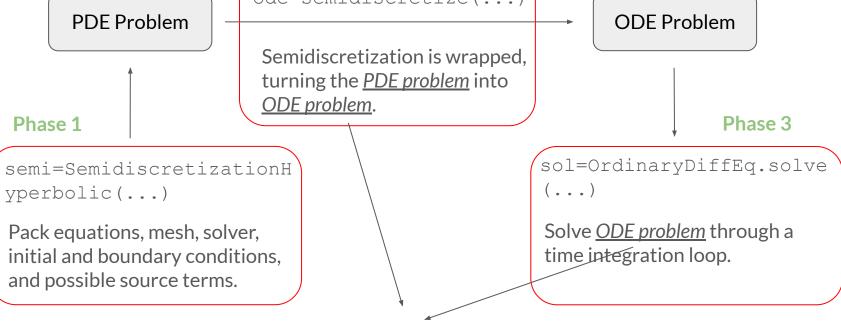

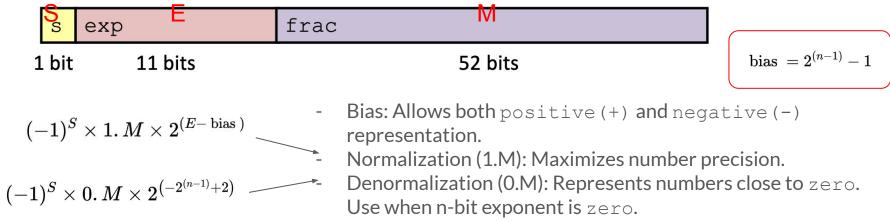

Single precision (float/Float32): 32 bits

Double precision (double/Float64): 64 bits

Case of 32-bit floating point (single/Float32)

- Float64 is converted to Float32 (CPU-GPU).

- The 52-bit mantissa (i.e., fraction) of the Float64 is truncated (or rounded) to fit into the 23-bit mantissa of the Float32.

Case of 64-bit floating point (double/Float64)

- Float64 is <u>NOT</u> converted to Float32 (CPU-GPU).

- But why are there still accuracy errors?

With <u>finite precision</u>, the order of number operation affect the accuracy of the final result. (See one toy example in the next slide!)

Toy example - <u>5-bit</u> number representation system

- The <u>smallest positive number</u> can be represented (i.e., precision) is

1\*2^ (-2) =0.25 (Can be easily verified!), and thus any number <u>less than</u>

0.25 will underflow to zero.

- Consider the following two calculations:

- (1)  $1.00*2^{0} + 1.00*2^{0} + 1.00*2^{(-2)} + 1.00*2^{(-2)} =$  $1.00*2^{1} + 1.00*2^{(-2)} + 1.00*2^{(-2)} = 1.00*2^{1}$

- (2)  $(1.00*2^{0} + 1.00*2^{0}) + (1.00*2^{(-2)} + 1.00*2^{(-2)}) = 1.01*2^{1}$

Both (1) and (2) are using binary!

# Remaining Precision Problems (How to deal with?)

#### Reasons have been identified!

Trade-off: Speed v.s. Precision

- GPU programming (i.e., parallel programming) adopt parallel computing strategy, that is, the order of operations <u>may not be sequential</u> (like summing up an array of numbers).

#### How to deal with this issue?

- (1) Easy approach: Sorting is frequently used in parallel numerical algorithms

- Group numerical values close to each other in the same group.

- Perform operation (e.g., addition) in each group, more likely to get accurate result.

- Sign of numbers should be taken into account.

- (2) Advanced approach: <u>Kahan's Summation Algorithm</u> (i.e., Compensated Summation Algorithm) Only for accurate summation.

# julia Remaining Precision Problems (Q&A)

Typically, there is a <u>trade-off between speed and precision</u>

- Use Float32/float, low precision but high speed

- Use Float64 /double, high precision but low speed -

Further nested trade-off problem (can be applied to both 32-bit and 64-bit)

- Apply algorithm, improve precision but affect speed

- No algorithm, keep errors and speed

Which one is more preferable, and what level of accuracy error is acceptable? (Given the context of solving PDE problems.)

**Relative Error Formula**

$$\delta = \left|rac{v_A - v_E}{v_E}

ight| \cdot 100\%$$

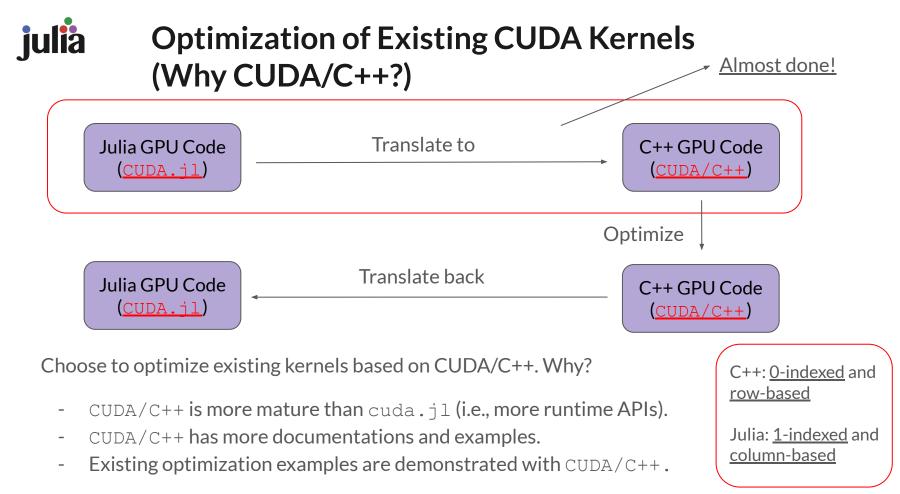

### **Optimization of Existing CUDA Kernels** (Some Reviews)

Recall what I have said in the <u>GSoC project report</u>...

- Implement custom CUDA kernels instead of using existing types (e.g., CuArray type).

- Avoid using conditional statement (e.g., if-then-else branches) in CUDA kernels.

- Decrease the number of CUDA kernel calls (i.e., calls to \_\_\_\_\_\_global\_\_\_functions) within a certain function (i.e., \_\_host\_\_\_function).

But these are not enough...

- We have to further optimize CUDA kernels!

|                           | Executed on the: | Only callable from the: |

|---------------------------|------------------|-------------------------|

| device float DeviceFunc() | device           | device                  |

| globalvoid KernelFunc()   | device           | host                    |

| host float HostFunc()     | host             | host                    |

<u>performed</u> /  $\frac{\#(times of accessing to global memory)}{\#(times of modeling-point calculation)}$

#### julia **GPU** Memory Architecture/Layout (Kernel Optimization) Complicated... but...

#### **Good Performance**

**Registers** - Thread scop Fastest - Very limited

Shared memory - Block Fast - Limited

Global memory - Grid se (GPU device) -Varia Slow - Not limited

#### **Bad Performance**

| And | <pre>cudaMalloc()</pre> |

|-----|-------------------------|

|-----|-------------------------|

| scope -                               | Device code can:                                                                                                         |                                                 |        | X           | Grid                                                  |                                                                 |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------|-------------|-------------------------------------------------------|-----------------------------------------------------------------|

| ed                                    |                                                                                                                          | per-thread registers<br>per-thread local memory |        |             | Block (0, 0)                                          | Block (0, 1)                                                    |

| lock scope -                          | <ul> <li>R/W per-block shared memory</li> <li>R/W per-grid global memory</li> <li>Read only per-grid constant</li> </ul> |                                                 |        | ory         | Shared Memory<br>Registers<br>Registers               | Shared Memory<br>Registers<br>Registers                         |

| rid scope                             | memor                                                                                                                    | ту                                              |        |             | Thread         Thread           (0, 0)         (1, 0) | Thread<br>(0, 0)         Thread<br>(1, 0)           v         v |

| Variable declaration                  |                                                                                                                          | Memory                                          | Scope  | Lifetime    | Global                                                | Memory                                                          |

| Automatic variables other than arrays |                                                                                                                          | Register                                        | Thread | Kernel      | v v<br>Constan                                        | t Memory                                                        |

| Automatic array variables             |                                                                                                                          | Local                                           | Thread | Kernel      |                                                       |                                                                 |

|                                       | int SharedVar;                                                                                                           | Shared                                          | Block  | Kernel      |                                                       |                                                                 |

| deviceint GlobalVar;                  |                                                                                                                          | Global                                          | Grid   | Application | Reside ir                                             | nglobal memory!                                                 |

| deviceconstant_                       | _ int ConstVar;                                                                                                          | Constant                                        | Grid   | Application |                                                       | 1                                                               |

## julia GPU Memory Architecture/Layout Cont'd (Kernel Optimization)

| cudaMalloc(), thus they are in global memory.                                                                       |

|---------------------------------------------------------------------------------------------------------------------|

| oat* output, int size) {                                                                                            |

| Same for our du and u variables!                                                                                    |

| Recall that allocating whole arrays<br>is not allowed in Julia (CUDA.j1).<br>Why?<br>- Use shared memory is better. |

|                                                                                                                     |

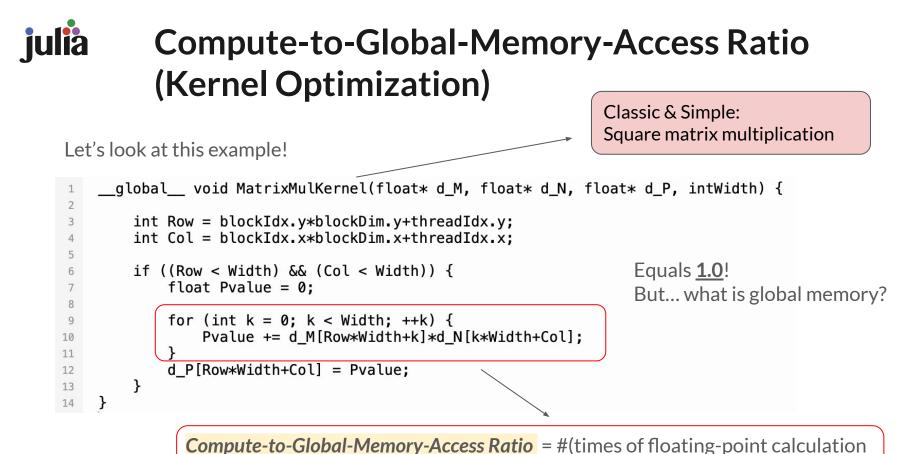

### **Optimization of Existing CUDA Kernels** (Insights from Ratio...)

Check the formula again:

**Compute-to-Global-Memory-Access Ratio** = <u>#(times of floating-point calculation</u> performed) / <u>#(times of accessing to global memory)</u> within a program region

- Higher ratio implies better performance

- Lower ratio implies worse performance

Generally there are two ways (straightforward!)

- Increase numerator (But almost fixed...)

- Decrease denominator (1) Use registers (2) Use shared memory (3) Keep in global memory

Common approach by programmers!

Have to increase the ratio! But how?

### Optimization of Existing CUDA Kernels (Insights from Ratio...)

How to decrease denominator (i.e., decrease the times of accessing global memory):

- Use registers (Very limited! <u>Cannot</u> allocate large amounts of data...)

- Use shared memory (Viable!)

- Keep in global memory (Viable!)

```

__global__ void MatrixMulKernel(float* d_M, float* d_N, float* d_P, intWidth) {

1

2

int Row = blockIdx.y*blockDim.y+threadIdx.y;

3

int Col = blockIdx.x*blockDim.x+threadIdx.x;

5

if ((Row < Width) && (Col < Width)) {

6

float Pvalue = 0;

7

8

for (int k = 0; k < Width; ++k) {

9

Go back to our

Pvalue += d M[Row*Width+k]*d N[k*Width+Col];

10

}

11

previous example!

d P[Row*Width+Col] = Pvalue;

12

}

13

14

```

Still confused? No worries!

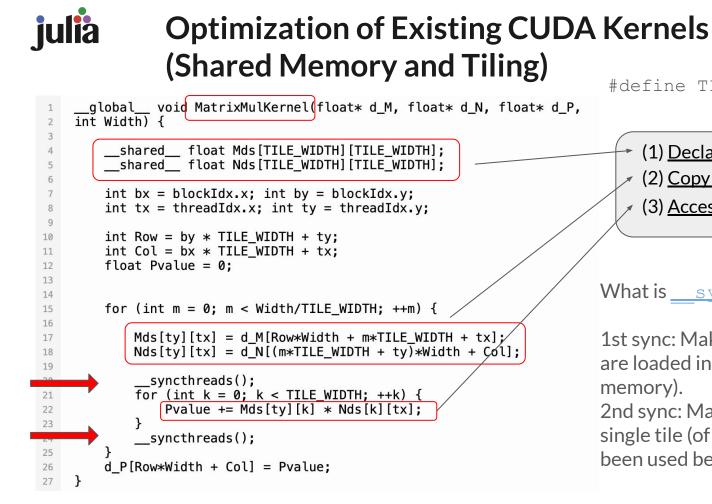

#define TILE WIDTH ...

What is <u>syncthreads ()</u>?

(1) <u>Declare shared memory</u>

(2) <u>Copy from global to shared</u>

(3) Access to shared memory

1st sync: Make sure all necessary data are loaded into a single tile (of shared memory).

2nd sync: Make sure all data from a single tile (of shared memory) have been used before being replacing.

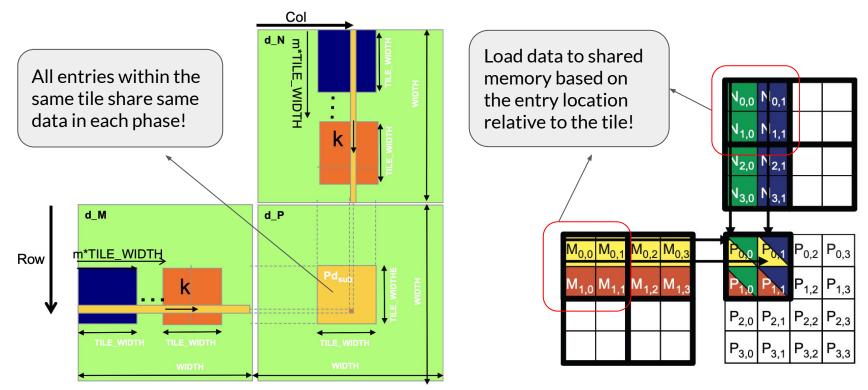

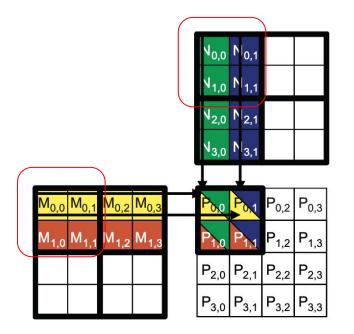

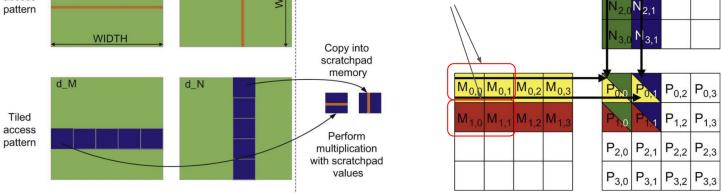

#### Optimization of Existing CUDA Kernels (Shared Memory and Tiling)

Do some visualization!

### Optimization of Existing CUDA Kernels (Shared Memory and Tiling)

#(new times of accessing global memory)

= #(original times of accessing global memory)/TILE\_WIDTH

Global memory accessing be reduced by times! But what is the <u>best size</u> for tiling?

### Optimization of Existing CUDA Kernels (About Size for Tiling...)

Within the limit, the larger the better? Not really... Need performance tuning.

Consider the following extreme cases:

- If size for tiling is too large, we will exceed <u>the limit of shared memory per</u> <u>block</u>.

- If size for tiling is too small, we will have few performance improvement.

The best size actually depends on the <u>matrix</u> <u>size</u> and the <u>GPU architecture</u>. And the tile size often <u>matches block size</u>.

Fortunately, programmers can dynamically allocate shared memory during runtime!

#### CU\_DEVICE\_ATTRIBUTE\_MAX\_SHARED\_MEMORY\_PER BLOCK CU\_DEVICE\_ATTRIBUTE\_WARP\_SIZE CU\_DEVICE\_ATTRIBUTE\_MAX\_THREADS\_PER\_BLOCK ...

### Optimization of Existing CUDA Kernels (Dynamic allocation of Shared Memory) Case dependent!

Let's start with kernel configuration and execution.

// Get CUDA devices...

cuDeviceGetAttribute(&maxSharedMemPerBlock,

CU\_DEVICE\_ATTRIBUTE\_MAX\_SHARED\_MEMORY\_PER\_BLOCK, cuDevice);

cuDeviceGetAttribute(&maxThreadsPerBlock,

CU\_DEVICE\_ATTRIBUTE\_MAX\_THREADS\_PER\_BLOCK, cuDevice);

size\_t sizeShared;

int tileWidth

calculate\_appropriate\_SM\_usage(&sizeShared, &tileWidth,

maxSharedMemPerBlock, maxThreadsPerBlock, width, ...);

matrixMulKernel<<<dimGrid, dimBlock, sizeShared>>>(Md, Nd, Pd, Width,

tileWidth);

Get the <u>tile size</u> (and thus <u>the size of</u> <u>shared memory</u>) based on some constraints:

- Tile memory cannot exceed maxSharedMemPerBlock.

- Block size cannot exceed maxThreadsPerBlock.

- Tile size (i.e., tileWidth) should be smaller than matrix size (i.e., width).

What else ...?

Launch up the kernel by passing the size of shared memory...

Warning: Shared memory configurator <u>should not</u> <u>be too complex</u>! Bad performance again!

### **Optimization of Existing CUDA Kernels** (Dynamic allocation of Shared Memory)

```

_global__ void MatrixMulKernel(float* d_M, float* d_N, float* d P,

int Width, int tileWidth) {

Then go quick with the kernel

2

3

implementation.

extern shared float shared[];

4

5

float* Mds = (float*)shared:

6

7

float* Nds = (flaot*)&Mds[tileWidth * tileWidth]:

8

9

int bx = blockIdx.x; int by = blockIdx.y;

int tx = threadIdx.x; int ty = threadIdx.y;

10

11

int Row = by * tileWidth + ty;

12

int Col = bx * tileWidth + tx:

13

float Pvalue = 0:

14

Check CUDA programming

15

for (int m = 0; m < Width/tileWidth; ++m) {</pre>

16

shared references here!

17

Mds[ty][tx] = d M[Row*Width + m*tileWidth + tx];

18

Nds[ty][tx] = d N[(m*tileWidth + ty)*Width + Col];

19

20

syncthreads();

21

for (int k = 0; k < tileWidth; ++k) {

22

Pvalue += Mds[ty][k] * Nds[k][tx];

23

24

syncthreads();

25

26

d P[Row*Width + Col] = Pvalue;

27

28

```

# julia Optimiz

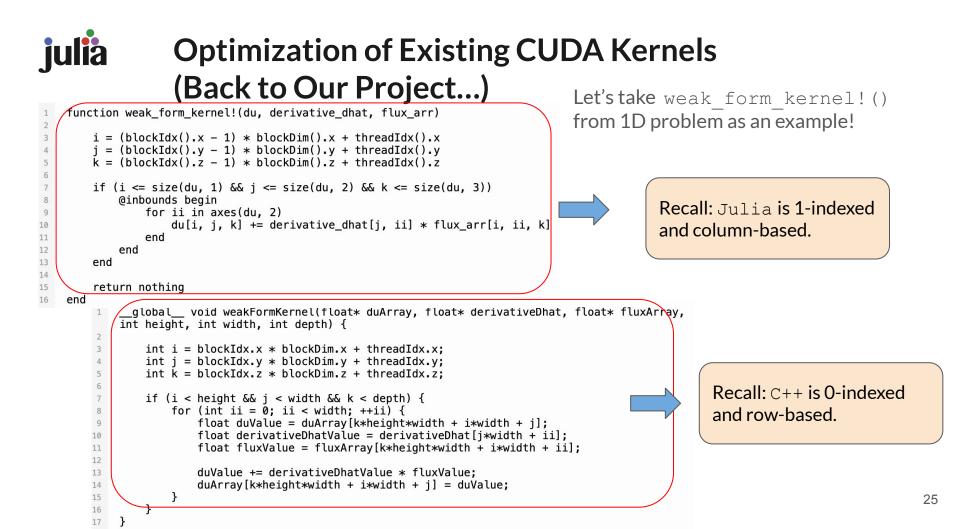

### Optimization of Existing CUDA Kernels (Back to Our Project...) Do some optim

#define TILE\_WIDTH ...

Do some optimization (tiling via shared memory)!

```

int height. int depth) {

shared float derivativeDhatShared[TILE WIDTH][TILE WIDTH]

___shared___float_fluxArrayShared[TILE_WIDTH][TILE_WIDTH]

Tiling along row and column (i.e., index \pm

int bx = blockIdx.x; int by = blockIdx.y;

and \frac{1}{2}), keep layer (i.e., index k) intact.

int tx = threadIdx.x; int ty = threadIdx.y;

int laver = blockIdx.z * blockDim.z + threadIdx.z;

int Row = by * TILE_WIDTH + ty;

10

int col = bx * TILE WIDTH + tx;

11

float duValue = duArray[layer*height*width + Row*width + Col];

Boundary check! Matrix size

12

13

is a multiple of tile size?

for (int m = 0; m < ceil(width/(float)TILE WIDTH; ++m) {</pre>

14

15

if ((Col < width) && (m*TILE WIDTH+tx) < width)

16

derivativeDhatShared[ty][tx] = derivativeDhat[Col*Width + m*TILE_WIDTH + tx];

17

if ((Row < height) && (m*TILE WIDTH+tx) < width)

18

fluxArravShared[tv][tx] = fluxArrav[laver*height*width + Row*Width + m*TILE WIDTH + tx]:

19

20

syncthreads();

21

for (int k = 0: k < TILE WIDTH: ++K) {

22

duValue += derivativeDhatShared[tx][k] * fluxArrayShared[ty][k];

Further optimization

23

24

via dynamic allocation

___syncthreads();

25

26

of shared memory...

duArray[layer*height*width + Row*width + Col] = Pvalue;

26

27

28

```

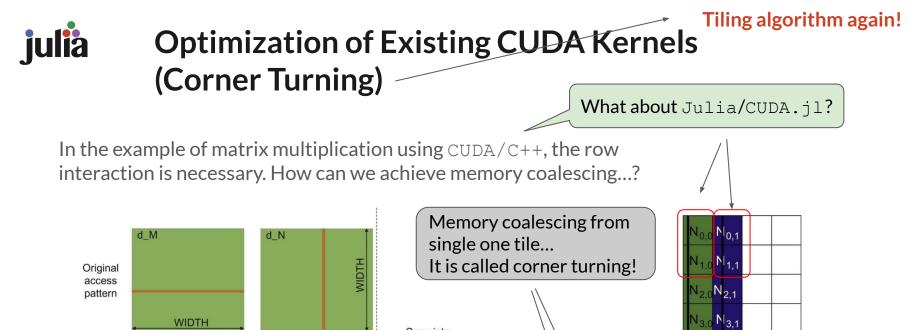

### Optimization of Existing CUDA Kernels (Memory Coalescing)

How to decrease denominator (i.e., decrease the times of accessing global memory):

- Use registers (Very limited! <u>Cannot</u> allocate large amounts of data...)

The global memory of a CUDA device is implemented with <u>DRAMs</u> (Dynamic Random-Access Memory).

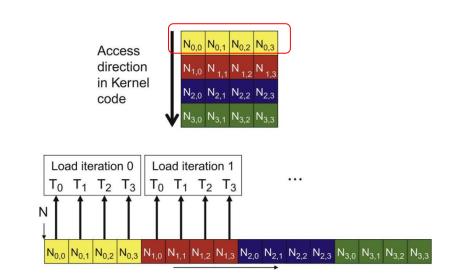

Each time a DRAM location is accessed, <u>a range of consecutive locations</u> that includes the requested location are actually accessed (i.e., DRAM burst).

#### Optimization of Existing CUDA Kernels (Memory Coalescing)

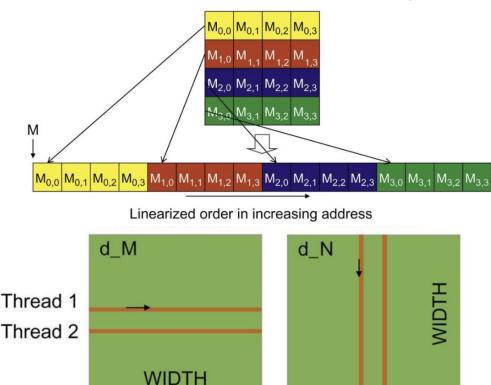

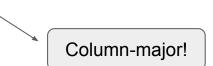

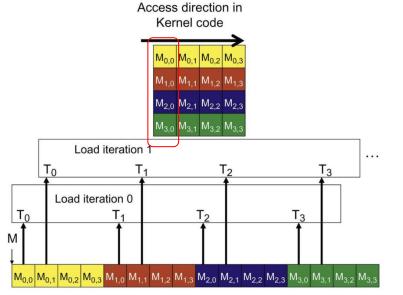

Array elements in C(C++) and CUDA are placed into linearly addressed memory space based on row-major convention.

What about Julia and CUDA.jl?

- Left is coalesced in CUDA.jl (Julia).

- Right is coalesced in CUDA (C++).

#### Optimization of Existing CUDA Kernels (Memory Coalescing Cont'd)

In a <u>row-based</u> layout, consecutive data is accessed at each iteration.

In a <u>column-based</u> layout, consecutive data is accessed at each iteration.

# Optimization of Existing CUDA Kernels (Short Summary)

To achieve a high compute-to-global-memory-access ratio, we adopt <u>tiling</u> <u>algorithm</u>, which bas basically has two advantages:

- The number of global memory loads is reduced due to the reuse of data in the shared memory.

- The renaming global memory loads are coalesced so the DRAM bandwidth utilization is further improved.

What else can we do ...?

Therefore, the main optimization strategy is to **apply the tiling algorithm** to our existing CUDA kernels.

Note that once the data is in the shared memory, they can be accessed either on a row basis or a column basis with much less performance variation because it is <u>high-speed on-chip memory</u>.

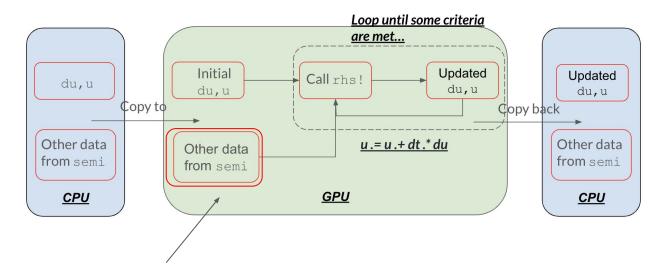

#### Optimization of Existing CUDA Kernels (About Sparse Matrix Computation...)

When solving the ODE problem, some data from semi (like cache.xx.xx) are sparse and remain unchanged during iteration (time integration).

A waste of memory bandwidth if zeros are doing nothing!

Kernel

# Sparse Matrix Parallel Computation (Some Brief Sketch)

Trade-off: Format transformation overhead v.s. Runtime speed

SpMV: Sparse Matrix-Vector CSR: Compressed Sparse Row How many loops? Does not make memory coalescing and SpMV/CSR Kernel incur control flow divergence in all warps. ELL: ELLPACK Padding and transposition Used for solving BVP One or a small number of rows have SpMV/ELL Kernel exceedingly large number of nonzero elements. Store rows separately JDS... COO: Coordinate Hybrid The padding overhead may still be significant SpMV/ELL-COO for the rest of rows.

- 1. Kirk, D. B., & Hwu, W. W. (2016). Programming Massively Parallel Processors: A Hands-on Approach (3rd ed.). Elsevier.

- NVIDIA. (n.d.). CUDA C Programming Guide. Retrieved December 18, 2023, from <u>https://docs.nvidia.com/cuda/cuda-c-programming-guide/contents.h</u> <u>tml</u>

- 3. Trixi.jl Developers. (n.d.). *Trixi.jl Documentation*. Retrieved December 18, from <u>https://trixi-framework.github.io/Trixi.jl/stable/</u>

- 4. CUDA.jl Developers. (n.d.). *CUDA.jl Documentation*. Retrieved December 18, from <u>https://cuda.juliagpu.org/stable/</u>

- 5. Amazon Web Services, Inc. (n.d.). AWS Documentation. Retrieved December 18, from <u>https://docs.aws.amazon.com/</u>

We have discussed a portion of the future work, focusing on the kernel optimization aspect.

Are there any questions so far?